JK Flip-Flop

A JK flipflop is a refinement of the SR flipflop, in which the indeterminate state of the SR type is defined in the JK type. Inputs J and K behave like inputs S and R to set and clear the flipflop (note that in a JK flipflop, the letter J is for set and the letter K is for clear). When logic 1 inputs are applied to both J and K simultaneously, the flip-flop switches to its complement state, ie., if Q=1, it switches to Q=0 and vice versa.

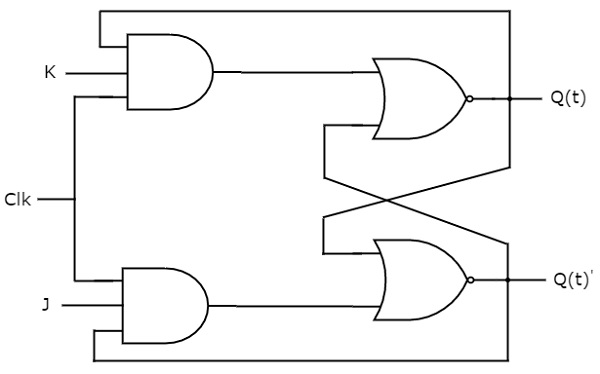

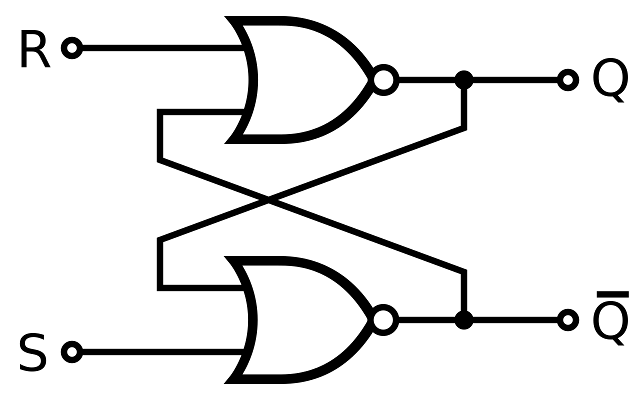

A clocked JK flip-flop is shown in Figure. Output Q is ANDed with K and CP input so that the flipflop is cleared during a clock pulse only if Q was previously 1. Similarly, output Q' is ANDed with J and CP input so that the flip-flop is set with a clock pulse only if Q' was previously 1. Note that because of the feedback connection in the JK flipflop, a CP signal which remains a 1 (while J=K=1) after the outputs have been complemented once will cause repeated and continuous transitions of the outputs. To avoid this, the clock pulses must have a time duration less than the propagation delay through the flip-flop. The restriction on the pulse width can be eliminated with a master-slave or edge-triggered construction. The same reasoning also applies to the T flip-flop presented next.

Transition

table of JK flipflop

|

Logic symbol of JK Flipflop |

A clocked JK flip-flop is shown in Figure. Output Q is ANDed with K and CP input so that the flipflop is cleared during a clock pulse only if Q was previously 1. Similarly, output Q' is ANDed with J and CP input so that the flip-flop is set with a clock pulse only if Q' was previously 1. Note that because of the feedback connection in the JK flipflop, a CP signal which remains a 1 (while J=K=1) after the outputs have been complemented once will cause repeated and continuous transitions of the outputs. To avoid this, the clock pulses must have a time duration less than the propagation delay through the flip-flop. The restriction on the pulse width can be eliminated with a master-slave or edge-triggered construction. The same reasoning also applies to the T flip-flop presented next.

|

| Logic Diagram of JK Flipflop |

|

Q

|

J

|

K

|

Q(t+1)

|

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

0

|

|

0

|

1

|

0

|

1

|

|

0

|

1

|

1

|

1

|

|

1

|

0

|

0

|

1

|

|

1

|

0

|

1

|

0

|

|

1

|

1

|

0

|

1

|

|

1

|

1

|

1

|

0

|

Comments

Post a Comment