SR Flip-Flop Circuit

Basic Flip-Flop Circuit:

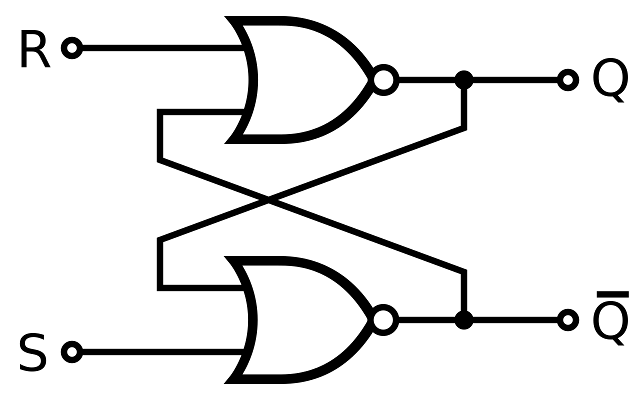

A flipflop circuit can be constructed from two NAND gates or two NOR gates. These flip-flops are shown in Figure 4.18 and 4.19. Each flip-flop has two outputs, Q and Q' and two inputs, set and reset. This type of flip-flop is referred to as an SR flipflop or SR latch. The flipflop in Figure has two useful states. When Q=1 and Q'=0, it is in the set state (or 1-state). When Q=0 and Q'=1, it is in the clear state (or 0-state). The outputs Q and Q' are complements of each other and are referred to as the normal and complement outputs, respectively. The binary state of the flip-flop is taken to be the value of the normal output.

|

| Logic diagram of SR Flipflop using NAND gates |

When a 1 is applied to both the set and reset inputs of the flip-flop in Figure , both Q and Q' outputs go to 0. This condition violates the fact that both outputs are complements of each other. In normal operation this condition must be avoided by making sure that 1's are not applied to both inputs simultaneously.

|

S

|

R

|

Q

|

Q’

|

|

1

|

0

|

1

|

0

|

|

0

|

0

|

1

|

0[after S=1,R=0]

|

|

0

|

1

|

0

|

1

|

|

0

|

0

|

0

|

1[after S=0,R=1]

|

|

1

|

1

|

0

|

0

|

Truth table of SR Flipflop

|

| Logic diagram of SR Flipflop using NAND gates |

|

S

|

R

|

Q

|

Q’

|

|

1

|

0

|

0

|

1

|

|

1

|

1

|

0

|

1[after S=1,R=0]

|

|

0

|

1

|

1

|

0

|

|

1

|

1

|

1

|

0[after S=0,R=1]

|

|

0

|

0

|

1

|

1

|

Truth table of SR Flipflop

The NAND basic flip-flop circuit in Figure operates with inputs normally at 1 unless the state of the flip-flop has to be changed. A 0 applied momentarily to the set input causes Q to go to 1 and Q' to go to 0, putting the flip-flop in the set state. When both inputs go to 0, both outputs go to 1. This condition should be avoided in normal operation.

Clocked SR FlipFlop

|

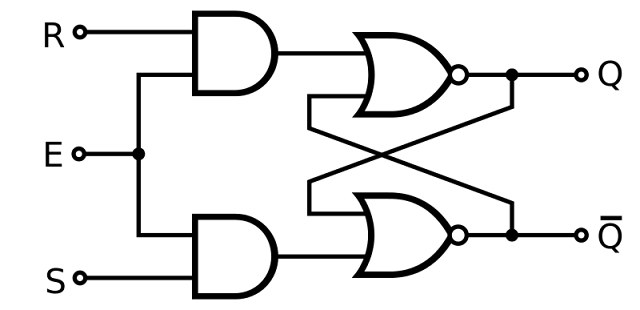

Logic diagram of Clocked SR Flipflop

|

The clocked SR flipflop shown in Figure consists of a basic NOR flipflop and two AND gates. The outputs of the two AND gates remain at 0 as long as the clock pulse (or CP) is 0, regardless of the S and R input values. When the clock pulse goes to 1, information from the S and R inputs passes through to the basic flip-flop. With both S=1 and R=1, the occurrence of a clock pulse causes both outputs to momentarily go to 0. When the pulse is removed, the state of the flip-flop is indeterminate, ie., either state may result, depending on whether the set or reset input of the flip-flop remains a 1 longer than the transition to 0 at the end of the pulse.

|

Q

|

S

|

R

|

Q(t+1)

|

|

0

|

0

|

0

|

0

|

|

0

|

0

|

1

|

0

|

|

0

|

1

|

0

|

1

|

|

0

|

1

|

1

|

indeterminate

|

|

1

|

0

|

0

|

1

|

|

1

|

0

|

1

|

0

|

|

1

|

1

|

0

|

1

|

|

1

|

1

|

1

|

indeterminate

|

Comments

Post a Comment